Address Translation

Assuming the virtual memory has 1024B, a page has 256B, then the index of page should be: \[\log_2{\frac{1024}{256}} = 2 bit\] So for an 32-bit address, the first 2 bits is the index, while the remaining 30 bits serve as offset.

Page Table

Consist of: [Valid] [Access Rights] [VPN] [PPN]

Valid bit determines whether this virtual page is mapped to a physical page. The mapping VPN to PPN is by looking up the table. The offset from virtual to physical is invariant.

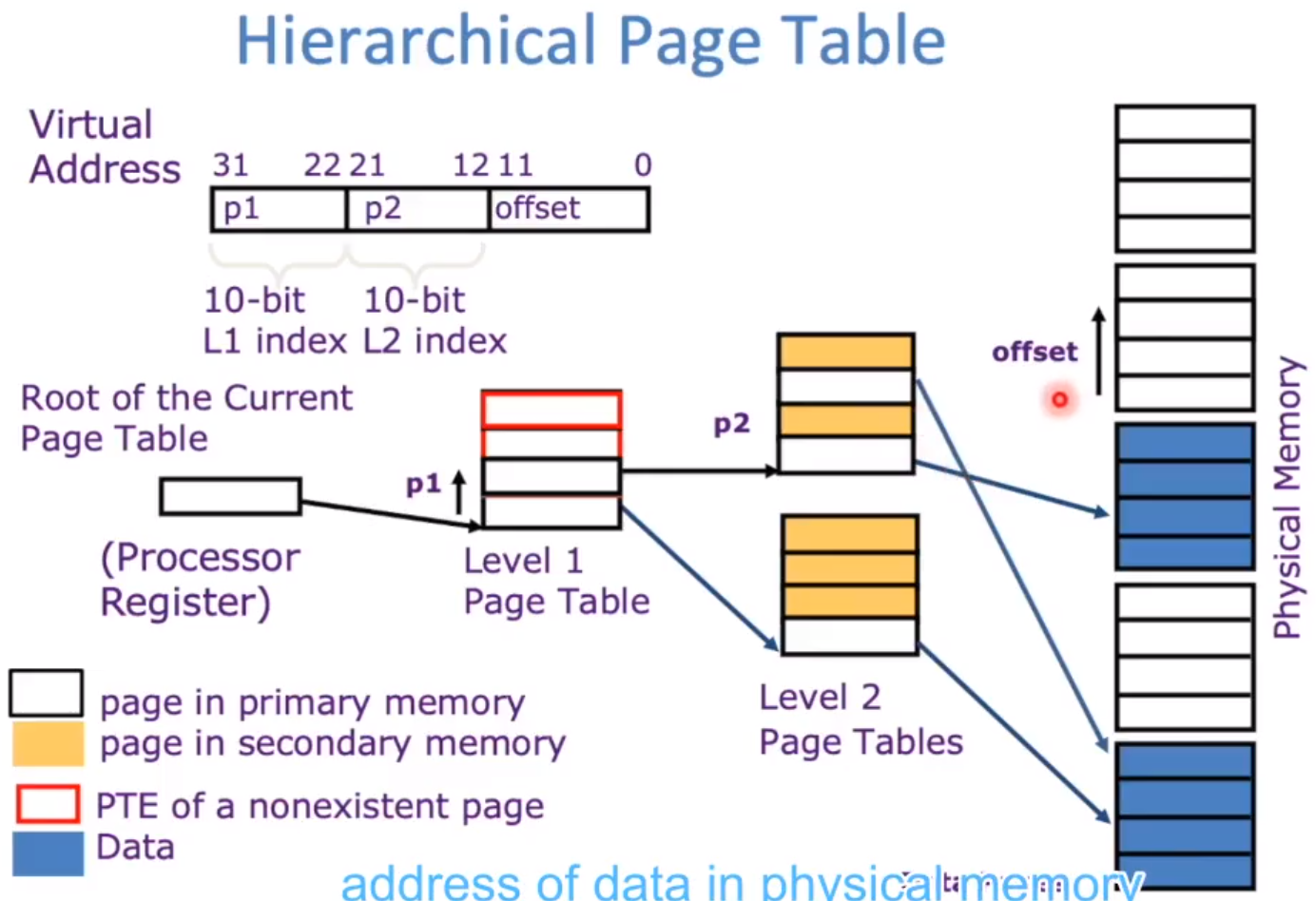

Page Tables are always saved in main memory. And we always create hierarchical page table since page tables is too big.

Problems

2+ Physical memory accesses per data access is too slow. Since locality in pages of data, there must be locality in the translations of those pages, we could build a separate cache for the page table.

For historical reasons, cache is called a Translation Lookaside Buffer (TLB)

VPN -> TLB -> PPN -> Data (Access Page Table in main memory if messed)

Performance Analysis

VM Performance

Similar to cache. But here, though the rate of page miss is much smaller, page miss will lead to much slower performance. Page fault(Loading page from disk) requires about 20,000,000 cycles, which is destructive. The corresponding miss rate must be quite small to match it.